Physics Division -- Fast Electronics Group

# Description and Instructions for the Firmware of Processing FPGA of the ADC250 Boards Version 0x0C09

9 June 2016

Hai Dong

# 1.0 Modifications:

#### Version 0x0C01

- 1. No pedestal subtraction for Hit (Code change)

- 2. Rewords Trigger Processing section (document change)

#### Version 0x0C02

- 1. ADC9230 result of Register read back is at Status 4. Page 11 section iv.

- 2. ADC\_CLK clock is 84 nS instead of 48 nS

Version 0x0C03

- 1. Took out ADC9230 result of Register read back.

- 2. At power up or after Hard Rest, Configures the ADC to accept negative going input.

## Version 0x0C05

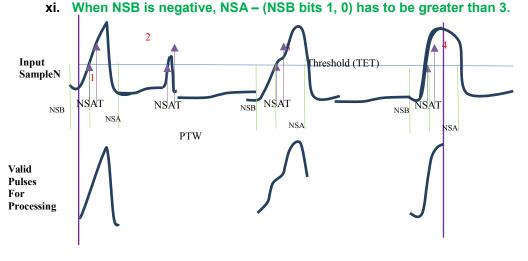

- 1. Added sections x, xi of Pulse Definition

- a. Fixed negative NSB

- b. When NSB is negative, the pulse is not valid if it cross threshold [NSB] + 2 samples before end of window

- c. When NSB is negative, NSA (NSB bits 1,0) has to be greater than 3.

#### Version 0x0C06

- TDC algorithm section iii: Implement V(N1) ≤ VMID < V(N1+1) instead of V(N1) < VMID ≤ V(N1+1) as was implemented in previous version.</li>

- Fix error in computing the number of ADC samples within NSB and NSA that are above threshold. (as described in <u>Time over threshold counter section</u>). The error is that when the pulse extended beyond window end, the number reported is over by one count.

#### Version 0x0C07

1. Fix problem with Configures the ADC to accept negative going input code. The problem is that the code does not recognize user configuration commands (Status 0 bit 0 is always zero).

## Version 0x0C08

- 1. Fix Time Quality Bit 2 so that it does not set when pulse peak is 2 samples before window end.

- 2. Fix Sync Reset so that it will reset the Time Stamp.

- 3. Fix Sync Reset so that it will not crash algorithm if it is issued during run.

#### Version 0x0C09

1.—Eliminate "When overflow bit (13) of any ADC sample of Pulse Duration is one (indicate the sample is overflowed or under-flowed), all sum bits are set to 1" in Pulse Sum description. Sum of ADC sample will be summed as usual.

2.

# 1.0 Introduction

This document will describe the latest, upgraded firmware version of the processing FPGA on the FADC250 board. The new version of the firmware will provide more processing, include monitoring capabilities and reduces the processing time and data size. It has 6 unique functions as follows:

- Read Out Processing

- Trigger Processing

- Monitoring

- IC Configuration

- Miscellaneous

- Housekeeping.

The FADC250 board and this firmware are running nominally at 250MHz clock rate and all the time references listed in this document are Number of Samples \* 4 nS. However the board and this firmware can also be ran at slower clock. In this case all the time references listed in this document are Number of Sample \* 1/clock.

# 2.0 Read Out Processing

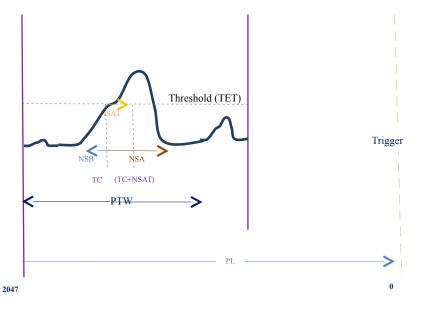

In Read Out Processing, the ADC samples are continuously stored in a 2048 sample Circular Raw Buffer (one per channel). When a trigger is received, a 12 bit Trigger Number counter is incremented and a number of ADC samples (Programmable Trigger Window) that are stored before (Programmable Lookback) the trigger is received is copied to the unprocessed Buffer. The Programmable Trigger Window (PTW) is user programmable from **5** to 511 (9 bits). The Programmable Lookback (PL) parameter is user programmable from 0 to 2047 (11 bits). After the PTW-number of ADC samples is copied to the unprocessed buffer, sample processing is based on the Processing Mode: Production Mode and Debug Mode.

Figure 1 : Read Out Processing

## 1. Production Mode (9).

In this mode, the algorithm detects pulses within the PTW number of samples stored in the unprocessed buffer. The samples of pulse(s) are summed and the time at which the pulse occurred within the PTW is calculated.

a. **Pulse Definition**. Pulse identification is initiated if a number of consecutive samples (NSAT) are above a programmable threshold (TET). The pulse duration (data set) includes the number of ADC samples before (NSB) and after (NSA) the first sample crossed threshold (TC). NSA

includes TC. The data set that defines the pulse includes only samples within the trigger window (PTW), even if NSB and NSA would extend beyond the window boundaries.

- i. Up to four distinct pulses may be detected within PTW samples. The Maximum Number of Pulses (MNoP) is programmable from 1 to 4. If PTW contains more than MNoP, only MNop pulses are reported.

- ii. NSA is programmable from Min 2 to 511 (9bits).

- iii. NSB is a 4 bit programmable parameter. When bit 3 is zero, bits 0-2 indicates the number of samples before TC to be included in Pulse Duration. When the bit 3 is one, bits 0-1 indicate the number of samples after TC to be excluded from Pulse Duration.

- iv. **NSA has to be greater than NSB when bit 3 is one**. When bit 3 is one only bits 0-1 are effective (bit 2 is ignored).

- v. Pulse duration = samples from MAX((TC-NSB),1) to MIN((TC+NSA-1), PTW) when NSB bit 3 = 0

- vi. Pulse duration = samples from (TC+NSB) to MIN((TC+NSB+NSA-1), PTW) when NSB bit 3 = 1.

- vii. Pulse number is counting from 1.

- viii. Pulse has to have at least one sample below (less than) TET to be considered the end to allow detection of a next pulse.

- ix. If the Pulse starts less than NSAT + 1 before the end of PTW, it is <u>NOT</u> counted as a pulse.

- x. When NSB is negative, if the pulse starts after [NSB] + 2 samples before end of window, it is **NOT** counted as a pulse.

Pulse 1 extends beyond the beginning of PTW Pulse 2 does not have NSAT number of samples above TET Pulse 4 extends beyond the end of PTW

#### Figure 2 : Pulse Definition

- b. Pulse Sum is sum of samples of the defined Pulse Duration. The resulting Sum is an 18 bit quantity. When a pulse falls outside PTW, the condition is reported in the Integral quality bits (3 bits). When the sum is overflowed, all sum bits are one. When overflow bit (13) of any ADC sample of Pulse Duration is one (indicate the sample is overflowed or under flowed), all sum bits are set to 1.

- i. When any of the sample is underflowed, integral quality bit 9 of integral word will be set

- ii. When any of the sample is overflowed, integral quality bit 10 of integral word will be set

- iii. When NSA falls outside the ending of PTW, integral quality bit 11 of integral word will be set.

- iv. <u>Time over threshold counter</u>: The number of samples where the FADC amplitude is larger than the readout threshold (TET) in the integration window will be reported in the data using 9 bits.

| Sum<br>Quality Bit | Functions                                   |

|--------------------|---------------------------------------------|

| 0                  | One or more sample is underflow             |

| 1                  | One or more sample is overflow              |

| 2                  | Set When NSA falls outside of window ending |

- c. **Pulse Pedestal** is the sum of a number of samples (NPED) after the beginning of PTW. NPED is programmable from 4 to 15 samples. When any of NPED samples is greater than a programmable max pedestal threshold (MaxPed) the Pedestal Quality bit 14 (shown in Appendix A) of Pedestal Sum is set.

- d. Time to Digital Converter (TDC)

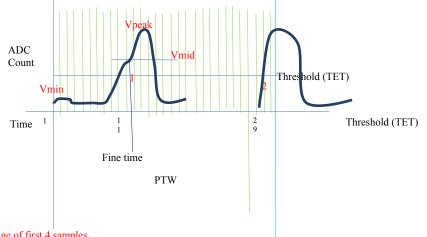

- i. The time reported represents the time on the pulse's leading edge where half of its maximum sampled amplitude is reached. The algorithm for computing this time is described below. Exceptional cases where the algorithm cannot be applied are also discussed. Whenever the algorithm fails, the reported time is the threshold crossing time TC. Information is returned that identifies these cases to the user.

- ii. A baseline amplitude (VMIN) is determined for the entire trigger window by averaging the first 4 samples of the trigger window. A pulse with threshold crossing sample number TC is identified in the manner discussed in the section on pulse definition. The peak amplitude (VPEAK) is determined by finding a sample beyond TC for which the sample value first decreases. The algorithm will search for VPEAK beyond the expected end of the pulse (TC + NSA). Cases for which no VPEAK is detected are discussed below.

- iii. The half amplitude (VMID = (VPEAK + VMIN) / 2)) of the pulse is computed. The sample number N1 is found on the leading edge of the pulse that satisfies:

- 1.  $V(N1) \le VMID < V(N1+1)$

- 2. where V(N1) and V(N+1) are the sample values of adjacent samples N1 and N1+1. N1 is reported as the coarse time.

- iv. The estimated time of occurrence of VMID between samples N1 and N1+1 is determined by a linear interpolation using their sample values V(N1) and V(N1+1). The time between samples (4 ns) is divided into 64 subsamples (62.5 ps each). In essence,

- 1.  $TF = 64^{*}(VMID V(N1)) / (V(N1+1) V(N1)).$

- 2. TF is reported as the fine time with values from 0 to 63. TF is reported in Fine Time bits 20-15 (Appendix A).

- 3. Coarse Time is the time of V(N1) and it is reported in Coarse Time bits 29-21 (Appendix A).

- v. If any of the first <u>5</u> samples is greater than MaxPed but less than TET, the TDC algorithm will proceed and Time Quality Bit 0 will be set to 1.

- vi. If any any of the first <u>5</u> samples is greater than TET or underflow, the TDC will NOT proceed.

- 1. pulse time is set to TC,

- 2. Pulse Peak is set to zero.

- 3. Time Quality bits 0 and 1 (appendix A) are set to 1.

- vii. A problem with the algorithm occurs if VPEAK is not found within the trigger window. In this case, the reported parameters are as followed:

- 1. Pulse time is set to TC.

- 2. Pulse Peak is set to zero.

- 3. Time Quality bit 1 (appendix A) is set to 1.

- viii. Vpeak is found when the current sample is less than the previous sample. Moreover this condition has to be met 1 sample before end of window.

- ix. If the pulse extended beyond the window, TC will be reported and Sum quality bit 2 is set.

- x. When Vpeak is beyond NSA, bit 2 will be set. TDC time is reported if condition viii is met. If condition viii is not met, TC is report and Time quality bit 1 is also set. When a pulse occurred close to end of window and Vpeak cannot be found this bit will also set.

- xi. Time reported is 15 bits and has a time resolution of 62 pico-seconds. The upper 9-bits are called the coarse time and the lower 6-bits are called the fine time. The fine time of

TC time is always zero. Both the coarse time of TC and TDC are starting from one. In other word the coarse time of the first sample of the PTW is one.

| Time<br>Quality Bit | Functions                                                         |

|---------------------|-------------------------------------------------------------------|

| 0                   | Set when any of the first 4 samples is greater than MaxPed or TET |

| 1                   | When Vpeak cannot be found                                        |

| 2                   | Pulse Peak is beyond NSA or could be beyond end of window         |

Vmin = Average of first 4 samples

| Pulse Time Co   | oarse Fine      | Pulse Time for pulse #1 is calculated as described above            |

|-----------------|-----------------|---------------------------------------------------------------------|

| Pulse $\#1 = 0$ | 00001011 100000 | Pulse Time for pulse #2 is set to TC because the pulse peak was not |

| Pulse $\#2 = 0$ | 00011101 000000 | found within PTW.                                                   |

#### Figure 3: TDC

#### e. To run Production Mode

- i. Set up Programmable Parameters

- ii. Write Config 1 as follow:

- 1. Bit 3 = 1 Accept and Process Trigger

- 2. Bit 5-4 = Max Number of Pulse in PTW to process

- 3. Bit 7 = 1 to process data from ADC IC; 0 to process data from Play Back (see below)

- 4. Bit 9-8 = 01

#### f. To change to Debug Mode

- i. Write Config 1 as follow:

- 1. Bit 3 = 0 Stop Accepting trigger

- 2. Bit 5-4 = Max Number of Pulse in PTW to process

- 3. Bit 7 = 1 to process data from ADC IC; 0 to process data from Play Back (see below)

- 4. Bit 9-8 = 01 Do not change mode yet

- ii. Wait For Done All Trigger Received by polling bit 15 of Status 1

- iii. Write Config 1 as follow:

- 1. Bit 3 = 1 Accept and process trigger

- 2. Bit 5-4 = Max Number of Pulse in PTW to process

- 3. Bit 7 = 1 to process data from ADC IC; 0 to process data from Play Back (see below)

- 4. Bit 9-8 = 10 change to Debug Mode

## 2. Debug Mode (10).

In addition to calculating Pulse Sum, Pulse Pedestal, TDC, Pulse Peak as described in Production Mode, this mode also reports all the samples in PTW if there is at least one pulse (NSAT number of samples greater than threshold) in the PTW.

- a. To run Debug Mode

- i. Set up Programmable Parameters

- ii. Write Config 1 as follow:

- 1. Bit 3 = 1 Accept and Process Trigger

- 2. Bits 5-4 = Max Number of Pulse in PTW to process

- 3. Bit 7 = 1 to process data from ADC IC; 0 to process data from Play Back (see below)

- 4. Bits 9-8 = 10

#### b. To change to Production Mode

- i. Write Config 1 as follow:

- 1. Bit 3 = 0 Stop Accepting trigger

- 2. Bits 5-4 = Max Number of Pulse in PTW to process

- 3. Bit 7 = 1 to process data from ADC IC; 0 to process data from Play Back (see below)

- 4. Bits 9-8 = 10 Do not change mode yet

- ii. Wait For Done All Trigger Received by polling bit 15 of Status 1

- iii. Write Config 1 as follow:

- 1. Bits 3 = 1 Accept and process trigger

- 2. Bits 5-4 = Max Number of Pulse in PTW to process

- 3. Bits 7 = 1 to process data from ADC IC; 0 to process data from Play Back (see below)

- 4. Bits 9-8 = 01 change to Debug Mode

#### 3. Read Out Programmable Parameters.

| Name   | Number<br>Of Bits | Functions                                                                                                                                                                                                                               |

|--------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PTW    | 9                 | <b>PTW+1</b> number of ADC samples to be processed per trigger.<br><b>Min is 6. Must be &gt; NPED</b>                                                                                                                                   |

| PL     | 10                | Number of ADC samples back from trigger point to beginning of PTW                                                                                                                                                                       |

| NSB    | 4                 | <ul> <li>When bit 3 = 0, bits 2-0 is the number of ADC samples from Threshold Crossing (TC) to be included in Pulse Sum.</li> <li>When bit 3 = 1, bits 1-0 is the number of ADC samples from TC to be excluded in Pulse Sum.</li> </ul> |

| NSA    | 9                 | Number of ADC samples after TC to be included in Pulse<br>Sum. NSA includes TC Sample. Min is 2                                                                                                                                         |

| TET    | 1                 | Trigger Energy Threshold. A pulse is considered to be valid<br>when a number of consecutive ADC samples (NSAT) are<br>above TET                                                                                                         |

| NSAT   | 2                 | Number of consecutive ADC samples that have to be above<br>TET before a pulse is valid. 0-> 1 sample 1-> 2 samples 2-<br>>3samples 3->4samples                                                                                          |

| MNoP   | 2                 | Maximum number of pulses that will be processed. 0 $\_$ 1 1 $\_$ 2 $\_$ 3 3 $\_$ 4                                                                                                                                                      |

| NPED   | 4                 | NPED + 1 number of sample to sum up for Pulse Pedestal.<br>Min is 4 Max is 15. NPED has to be less than PTW.                                                                                                                            |

| MaxPed | 10                | ADC Samples have to be below this Max Pedestal value to be valid to be included in read back pedestal sum.                                                                                                                              |

Failure to adhere to Min values can result in unpredictable results.

## 4 Read Out Data Output.

Read Back data is written out to the External FiFo to be read by the Control FPGA. The data written out includes Trigger Number, Time at which the Trigger received, and Mode 9 or 10 data. The format is shown in Appendix A.

# 3.0 Trigger Processing

In Trigger Processing, the ADC samples are processed and sent to the Control FPGA to be sent to the Crate Trigger Processor (CTP). There are two functions: Trigger Sum and Trigger Hit Bits.

## 1. Trigger Pedestal Subtraction

Each ADC channel has a programmable Trigger Path Pedestal Subtract Value (TPSV). The TPSV is subtracted from every ADC sample. For ADC samples that are smaller than TPSV, the difference is set to zero. The differences are input to Trigger Sum.

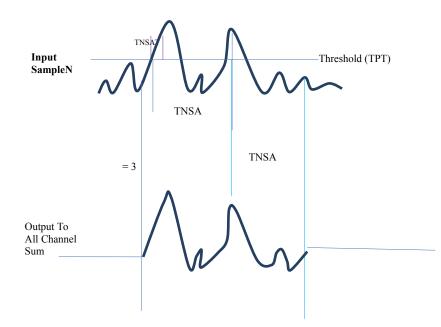

#### 2. Trigger Sum.

When a number of consecutive <u>ADC Samples</u> are greater than a programmable Trigger Path Threshold (TPT), <u>three differences</u> before and a TNSA number of differences after the 1st <u>ADC Sample</u> are sent to summing code. If at the end of TNSA samples, the immediate ADC sample is greater than TPT, another TNSA differences are sent. If at the end of TNSA samples, the immediate <u>ADC sample</u> is less than TPT, zeroes are sent. When 2 consecutive pulses are piling up, overlapping differences are not sent to summing code. In other words differences are only sent once. The summing code added differences and/or zeroes from all 16 ADC channels. Each ADC channel has individual TPSV values. One TPT value covers all ADC channels. Figure 3 show an example of differences "filtering"

Figure 4. Example for Trigger Sum Sample Processing Code:

## 3. Trigger Hit Bit.

When the differences are greater than TPT, Hit Bit goes high. There is one hit bit per ADC channel

## 4. Trigger Processing Programmable Parameters.

| Names | Number<br>Of Bits | Functions                                                                                                                                                                                 |

|-------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPSV  | 12                | Trigger Path Pedestal Subtract Values are subtracted from<br>ADC samples. The different ADC samples are sent to Trigger<br>Sum and Hit Bits. Each ADC channel has TPSV (total 16<br>TPSV) |

| TPT   | 12 | When a number of consecutive ADC differences (TNSAT) are<br>greater than Trigger Path Threshold (TPT), three before and<br>TNSA differences ADC samples are sent to summing code.<br>One TPT for all 16 ADC channels. |

|-------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TNSAT | 2  | Number of consecutive ADC differences that have to be<br>above TPT before a pulse is valid. 0-> 1 sample 1-> 2<br>samples 2->3samples 3->4samples                                                                     |

| TNSA  | 6  | Number of ADC differences after the first TPT crossing.                                                                                                                                                               |

# 4.0 Monitoring

## 1. Pedestal Sum

For each ADC channel, the sum of a programmable number unprocessed ADC samples can be read. When a read pedestal request is received from Control FPGA, it does the following for each ADC channel:

- 1. Capture a programmable number of unprocessed ADC samples (MNPED). These are not consecutive samples.

- 2. Sum up these samples. When any of MNPED samples is greater than a programmable max pedestal threshold (PMaxPed) or less than zero (ADC bit 13 is 1 and bit 0-12 are zeroes), bit 14 of the 14 bits (13-0) Sum will be set.

- 3. When sum is done, bit Monitored Pedestal Sum Done is set to 1. The time taken for summing is (MNPED + 3 + 2) \* 1/Clock.

- 4. Host reads all 16 Sums at register <u>STATUS2</u>. All 16 sums are mapped to only one register. The first read will be sum of ADC channel 1, follow by sums of channels 2,3,...,16. Monitored Pedestal Sum Done bit will ReSet to 0.

- 5. The Pedestal Sum only monitors ADC Sample. It does not monitor PlayBack value.

- 6. To Read Monitored Pedestal Sums

- a. Reset Monitored Pedestal Sum Request bit (Config1 Bit 15)

- b. Set Monitored Pedestal Sum Request bit

- c. Poll Monitored Pedestal Sum Done Bit (STATUS2 Bit 15) for a one

- d. Read STATUS2 16 times for Pedestal Sums of ADC channel 1,..., 16

| •• | Monitoring i co | cotal Oulli I |                                                                                                           |  |  |  |

|----|-----------------|---------------|-----------------------------------------------------------------------------------------------------------|--|--|--|

|    | Names           | Number        | Functions                                                                                                 |  |  |  |

|    |                 | Of Bits       |                                                                                                           |  |  |  |

|    | MNPED           | 4             | <b>MNPED + 1</b> number of sample to sum up for Pulse Pedestal for Monitoring. <b>Min is 4</b> Max is 15. |  |  |  |

|    | PMaxPed         | 10            | When an ADC Samples is greater than this, <b>bit 14 of the 14 bits (13-0) Sum will be set.</b>            |  |  |  |

## 2. Monitoring Pedestal Sum Programmable Parameters

## 3. FPGA Die Temperature

The temperature of the FPGA die can be read at register STATUS3 (Die Temp). The Celsius temperature is calculated as follow:

DieTemp\_C = ((float)(STATUS3 >> 6) \* 503.975/1024) - 273.15;

## 4. Firmware Version Number

Firmware version number can be read at register STATUS1 bits 14 to 0. Bits 14-8 is 0x0C and bits 7-0 indicates the code revision

## 5. Trigger Number 12 bits

The present Trigger Number is also available at register STATUS1.

## 6. STATUS Register

| Number<br>Of Bits | Functions                                       |  |  |  |  |

|-------------------|-------------------------------------------------|--|--|--|--|

| 16                | Bits 14 to 0: Code Version                      |  |  |  |  |

|                   | Bit 15: 1= Command can be sent to AD9230        |  |  |  |  |

| 16                | 15 👝 1 Done process all Trigger received        |  |  |  |  |

|                   | 11-0 _ Trigger Number                           |  |  |  |  |

| 16                | Monitored Pedestal Sum.                         |  |  |  |  |

|                   | Bit 15 👝 1 Done computing Pedestal Sums.        |  |  |  |  |

|                   | Bit 14 👝 0 Pedestal Sum O                       |  |  |  |  |

|                   | 1. 1 one or more ADC Sample is/are out of bound |  |  |  |  |

|                   | Bit 13-0 👝 Sum of ADC Samples                   |  |  |  |  |

| 16                |                                                 |  |  |  |  |

|                   | FPGA Die Temperature                            |  |  |  |  |

| 16                | 7-0 Content of ADC register read back           |  |  |  |  |

|                   | Number<br>Of Bits<br>16<br>16<br>16<br>16       |  |  |  |  |

# 5.0 IC Configuration

# 1. ADC IC AD9230

The ADC AD9230 ICs are needed to be configured after power up.

- a. To configure all ADC ICs at one time

- i. Poll bit 15 of Status 0 for a one. This indicates firmware is ready to accept command.

- ii. Write 0 to bit 7 of Config 4. Rising edge firmware sends data to AD9230

- **iii.** Select register of AD9230 to write to by writing to bits 15-8 of Config 5. Write data to be written to register of AD9230 by writing bits 7-0 of Config 5.

- **iv.** Set bits 7,6 and reset Bit 5 of Config 4. Bit 6 tells firmware to write to AD230. Bit 5 tells firmware to write to all AD9230

- **b.** For Example to configure all ADC to convert negative going signal:

- i. Configure AD9230 delay clock

- 1. Poll bit 15 of Status 0 for a one.

- 2. Reset bit 7 of Config 4

- 3. 0x17 to bits 15-8 of Config 5 to select AD9230 ADC\_CLK\_OUT\_DELAY\_REG

- 0x9E to bits 7-0 of Config 5. Data to write to ADC\_CLK\_OUT\_DELAY\_REG 0x9E. Delay clock b

- 5. Set bit 7 and 6, reset bit 5 of Config 4. This tells firmware to write to AD9230

- 6. Poll bit 15 of Status 0 for a one

- 7. Reset bit 7 of Config 4

- 8. 0xFF to bit 15-8 of Config 5 to select ADC\_MASTER\_TO\_SLAVE\_REG

- **9.** 0x01 to bit 7-0 of Config 5. Data to write to ADC\_MASTER\_TO\_SLAVE\_REG. Tell AD9230 to execute delay clock setting.

- **10.** Set bit 7 and 6, reset bit 5 of Config 4

- **ii.** Configure AD9230 to run in CML mode

- **1.** Poll bit 15 of Status 0 for a one.

- 2. Reset bit 7 of Config 4

- 3. 0x0F to bits 15-8 of Config 5 to select AD9230 ADC\_AIN\_CONFIG\_REG

- **4.** 0x02 to bits 7-0 of Config 5. Data to write to ADC\_AIN\_CONFIG\_REG. Run in CML mode

- 5. Set bit 7 and 6, reset bit 5 of Config 4. This tells firmware to write to AD9230

- 6. Poll bit 15 of Status 0 for a one

- 7. Reset bit 7 of Config 4

- 8. 0xFF to bit 15-8 of Config 5 to select ADC\_MASTER\_TO\_SLAVE\_REG

- **9.** 0x01 to bit 7-0 of Config 5. Data to write to ADC\_MASTER\_TO\_SLAVE\_REG. Tell AD9230 to execute delay clock setting.

- **10.** Set bit 7 and 6, reset bit 5 of Config 4

- iii. Tell AD9230 to turn off test mode

- **1.** Poll bit 15 of Status 0 for a one.

- 2. Reset bit 7 of Config 4

- 3. 0x0D to bits 15-8 of Config 5 to select AD9230 ADC\_TEST\_REG

- **4.** 0x00 to bits 7-0 of Config 5. Data to write to ADC\_TEST\_REG. Turn off test mode

- 5. Set bit 7 and 6, reset bit 5 of Config 4. This tells firmware to write to AD9230

- 6. Poll bit 15 of Status 0 for a one

- 7. Reset bit 7 of Config 4

- 8. 0xFF to bit 15-8 of Config 5 to select ADC\_MASTER\_TO\_SLAVE\_REG

- **9.** 0x01 to bit 7-0 of Config 5. Data to write to ADC\_MASTER\_TO\_SLAVE\_REG. Tell AD9230 to execute delay clock setting.

- **10.** Set bits 7 and 6, reset bit 5 of Config 4

# 6.0 Miscellaneous Functions:

#### 1. ADC Channel Disable

Each ADC channel has a bit that when set will zero the input to Trigger Sum and Trigger Hit Bits. Note, channels can be excluded from the readout if needed by setting readout thresholds (TET) to 4095. To disable (zeroes input to Trigger Sum and Hit Bit) an ADC channel, set the corresponding bit of Config 2 to 1.

#### 2. Sync\_reset

When Sync\_reset signal from Control FPGA is high and bit 15 of Config 3 is 0, the following signals are in RESET (zeroes):

- **1.** Time Stamp

- **2.** Trigger Number

- **3.** Not accepting Trigger signal from Control FPGA

#### 3. Soft Reset

When Soft Reset signal from Control FPGA is asserted low, everything EXCEPT Configuration Registers and AD9230 is reset.

#### 4. Hard Reset

When Hard Reset signal from Control FPGA is asserted low, everything is Set to values shown in Appendix C. All AD9230 ICs are reset to power state.

#### 5. Play Back

User defines pulses maybe injected into the processing pipeline using a playback feature. Play Back stores 32, 13-bit ADC values in RAM and cycles through 32 ADC values when a Trigger\_2 signal from Control FPGA goes from low to high. There are 16 Play Back, one per ADC Channel. All 512 ADC values are written into memory via Control Bus. Since all 512 ADC values occupy only one Control Bus address, all 512 values have to be written sequentially all at once The first 32 values are associated with ADC channel 0 and last 32 values are associated with ADC channel 15.

When **<u>bit 7 of Config 1</u>** is set, Play Back outputs (instead of ADC IC outputs) are applied to all processing functions of all ADC channels.

- a. To write 510 ADC values to RAM

- i. Put ADC value on bits 12-0 of Test Wave Form register. Set Bit 15.

- ii. Write Test Wave Form register

- iii. Read Test Wave Form register to verify that value is stored to RAM

- iv. Repeat above three steps for 510 values

- b. To write 511<sup>th</sup> and 512<sup>th</sup> ADC values to RAM

- i. Put 511<sup>th</sup> ADC value on bits 12-0 of Test Wave Form register. <u>ReSet</u> Bit 15.

- ii. Write Test Wave Form register

- iii. Read Test Wave Form register to verify that value is stored to RAM

- iv. Repeat above three steps for 512<sup>th</sup> values

# 7.0 House Keeping:

## 1. Control Bus

Registers and Status are accessed through Control Bus connected to FPGA. Control Bus is asynchronous 16 bits data bus. In the basic mode, Control Bus can access 65535 addresses. In extended mode the Control Bus can access up to 65,535 x 65,535 addresses by mean of secondary address feature (See FADC250 Program Manual)

- a. The signals of Control Bus are:

- i. ADR\_DAT = Address and Data

- ii. AS\_N = Address strobe

- iii. AK\_N = Address Acknowledge

- iv. DS\_N = Data strobe

- v. DK\_N = Data Acknowledge

- vi. RD\_N = Low indicate Read cycle

- vii. MS = Mode select

- viii. SS = Slave Status.

- b. To write to Register

- i. Control FPGA puts register's address on ADR\_DAT bus. Drives MS low

- ii. Control FPGA brings AS\_N low

- iii. Processing FPGA accept register's address. Drive SS low

- iv. Processing FPGA brings AK\_N low.

- v. Control FPGA puts register's value on ADR\_DAT bus

- vi. Control FPGA brings DS\_N low

- vii. Processing FPGA accept register's value

- viii. Processing FPGA brings DK\_N low.

- ix. Control FPGA drives DS\_N high

- x. Processing FPGA drives DK\_N high,

- xi. Control FPGA drives AS\_N high

- xii. Processing FPGA drives AK\_N high

- c. To read Register (Note Unused bits are read back as zeroes)

- i. Control FPGA puts register's address on ADR\_DAT bus. Drives MS low

- ii. Control FPGA brings AS\_N low

- iii. Processing FPGA accept register's address. Drive SS low

- iv. Processing FPGA brings AK\_N low.

- v. Control FPGA stops driving ADR\_DAT bus

- vi. Control FPGA brings DS\_N low.

- vii. Processing FPGA puts register's value on ADR\_DAT bus

- viii. Processing FPGA brings DK\_N low

- ix. Control FPGA accepts register's value.

- x. Control FPGA drives DS\_N high

- xi. Processing FPGA drives DK\_N high, Stop driving ADR\_DAT bus

- xii. Control FPGA drives AS\_N high

- xiii. Processing FPGA drives AK\_N high

# Appendix A: Data Format of FADC Processing

**Event Header** (2) – indicates the start an event.

(35 - 32) = 0001 (31) = 1 (30 - 27) = 2 (26 - 22) = 00000 (21 - 12) = trigger time (bits 9 - 0 (see below))(11 - 0) = trigger number

**Trigger Time** (3) – time of trigger occurrence relative to the most recent global reset. Time in the ADC data processing chip is measured by a 48-bit counter that is clocked by the 250 MHz system clock. The six bytes of the trigger time

Time =

$$T_A T_B T_C T_D T_E T_F$$

are reported in two words (Type Defining + Type Continuation).

Word 1:

$\begin{array}{l} (35-32)=0000\\ (31)=1\\ (30-27)=3\\ (26-24)=T_{C}\mbox{ bits }2-0\mbox{ (duplicated in Word 2)}\\ (23-16)=T_{D}\\ (15-8)=T_{E}\\ (7-0)=T_{F} \end{array}$

Word 2:

$\begin{array}{l} (35-32)=0000\\ (31)=0\\ (30-24)=reserved \mbox{ (read as 0)}\\ (23-16)=T_A\\ (15-8)=T_B\\ (7-0)=T_C \end{array}$

**Window Raw Data** (4) – raw ADC data samples for the trigger window. The first word identifies the channel number and window width. Multiple continuation words contain two samples each. The earlier sample is stored in the most significant half of the continuation word. Strict time ordering of the samples is maintained in the order of the continuation words. A *sample not valid* flag bit 13 will be set when PTW+1 is odd.

Word 1:

(35-32) = 0000 (31) = 1 (30-27) = 4 (26-23) = channel number (0 - 15) (22 - 12) = reserved (read as 0)(8-0) = PTW + 1 (window width (in number of samples))

Words 2 - N:

(35-32) = 0000 (31) = 0 (30) = reserved (read as 0) (29) = sample x not valid (28-16) = ADC sample x (includes overflow bit) (15-14) = reserved (read as 0) (13) = sample x + 1 not valid (12-0) = ADC sample x + 1 (includes overflow bit)

**Pulse Parameters** (9) – computed pulse parameters for detected pulses in a channel. The first word identifies the channel number, event number within the block, and pedestal information for the window. Multiple continuation word *pairs* contain information about the pulses detected. For a channel with hits detected:

Word 1: Channel ID and Pedestal information (reported *once* for a channel with hits)

- (35 32) = 0000

- (31) = 1

- (30 27) = 9

- (26 19) = event number within block (1 255)

- (18 15) =channel number (0 15)

- (14) = pedestal quality

- (13 0) = pedestal sum

Word 2 : Integral of first pulse in window

- (35 32) = 0000

- (31) = 0

- (30) = 1

- (29 12) = 18-bit sum of raw samples that constitute the pulse data set

- (11) = NSA extended beyond PTW

- (10) = One or more samples is overflow = 0x1FFF

- (9) = One or more sample is underflow = 0x1000

- (8-0) = number of samples within NSA that the pulse is above threshold

Word 3 : Time of first pulse in window

(35-32) = 0000 (31) = 0 (30) = 0 (29-21) = coarse time (4 ns/count) (20-15) = fine time (0.0625 ns/count) (14-3) = pulse peak (2) = Vpeak is beyond NSA or could be beyond window end (1) = Vpeak cannot be found(0) = 1 or more of first 4 samples is above either MaxPed or TET

Words 2 and 3 are repeated for each additional pulse found in the window for the channel.

Event Trailer: Indicate the end of an event. EVENT\_TRAILER = "0010" & X"E8000000";

<u>Note</u>: For maximum compression of data the Event Header (2) and Trigger Time (3) words may be suppressed from module readout in the Control FPGA (See Programming the FADC250)

# Appendix B: Example of Data Format for Production Mode 9

1<sup>st</sup> Trigger Occurred at Time 0x123456 Channel 1 and 15 has 1 good pulse each

Event Header (2) – indicates the start an event.

Word 1:

(35 - 32) = 0001 (31) = 1 (30 - 27) = 2 (26 - 22) = 00000 (21 - 12) = "00" & x"56" (trigger time (bits 9 -)) (11 - 0) = x"0001"

#### Trigger Time

$\begin{array}{l} \hline Word \ 2: \\ (35-32) = 0000 \\ (31) = 1 \\ (30-27) = 3 \\ (26-24) = "011" \\ (23-16) = x"4" \\ (15-8) = x"5" \\ (7-0) = x"6" \end{array} T_c \ bits \ 2-0 \ (duplicated \ in \ Word \ 2) \end{array}$

#### Word 3:

(35-32) = 0000 (31) = 0 (30-24) = 0 (23-16) = x"1" (15-8) = x"2"(7-0) = x"3"

#### **Pulse Parameters**

#### Channel 1 data

Word 4: Channel ID and Pedestal information (reported once for a channel with hits)(35 - 32) = 0000(31) = 1(30 - 27) = 9(26 - 19) = 00000000 event number within block (0 - 255)(18 - 15) = 0001(14) = 0(13 - 0) = pedestal sum0xC800----Word 5: Integral of first pulse in window(35 - 32) = 0000(31) = 0(30) = 1(29 - 12) = 18-bit sum of raw samples that constitute the pulse data set

(11 - 9) = 000

$(8-0)^{\prime}$  = number of samples within NSA that the pulse is above threshold

$\frac{\text{Word 6}}{(35-32)}$ : Time of first pulse in window (35 - 32) = 0000

(35-32) = 0000 (31) = 0 (30) = 0 (29-21) = coarse time (4 ns/count) (20-15) = fine time (0.0625 ns/count) (14-3) = pulse peak(2-0) = time quality

#### Channel 15 data

Word 7: Channel ID and Pedestal information (reported once for a channel with hits)

- (35 32) = 0000(31) = 1(30 - 27) = 9

- (26 19) = 00000000 event number within block (0 255)

- (18 15) = 1111

- (14) = 0

(13-0) = pedestal sum

$\underline{\text{Word 8}}$  : Integral of first pulse in window

- (35 32) = 0000

- (31) = 0

- (30) = 1

- (29 12) = 18-bit sum of raw samples that constitute the pulse data set

- (11 9) = 000

$(8-0)^{\prime}$  = number of samples within NSA that the pulse is above threshold

$\underline{\text{Word 9}}$  Time of first pulse in window

(35 - 32) = 0000 (31) = 0 (30) = 0 (29 - 21) = coarse time (4 ns/count) (20 - 15) = fine time (0.0625 ns/count) (14 - 3) = pulse peak(2 - 0) = time quality

**Event Trailer:** Indicate the end of an event. Word 10

EVENT\_TRAILER = "0010" & X"E8000000";

# Appendix C: Control Bus Memory Map for Registers Unused Bits are read back as zeroes

| Failure to adhere t | o Min val | ues can | result in u | npredic | table results |

|---------------------|-----------|---------|-------------|---------|---------------|

|                     |           |         |             |         |               |

|         |                 | 1        | 1      | 1                                                |                                | table results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|-----------------|----------|--------|--------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name    | Width<br>(Bits) | Quantity | Access | Primary<br>Address<br>(Secondar<br>y<br>Address) | Power<br>Up<br>Values<br>(hex) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| STATUS0 | 16              | 1        | R      | 0x0000<br>()                                     |                                | Bits 14 to 0: Code Version<br>Bit 15: 1= Command can be sent to<br>AD9230                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| STATUS1 | 16              | 1        | R      | 0x0001<br>()                                     |                                | 15 : 1 Done all Trig received<br>11-0 : TRIGGER NUMBER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| STATUS2 | 16              | 1        | R      | 0x0002<br>()                                     |                                | Monitored Pedestal<br>15 _ Sum is valid<br>14 _ 0 Sum OK. 1 One or more is out of<br>bound<br>13-0 _ Sum                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CONFIG1 | 16              | 1        | R/W    | 0x0003<br>()                                     | 0040                           | Bit 0-2 (old code process mode):<br>Bit 3: 1:Run<br>Bit 5-4 : Max Number of Pulses in Mode<br>10 and 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |                 |          |        |                                                  |                                | Bit 7: Test Mode (play Back).<br>Bit 8:<br>0 	mmode 9<br>1 	mmode 10<br>11-10 NSAT<br>13-12 TNSAT<br>15 	mmode Request Sum of Pedestal for<br>monitoring purpose                                                                                                                                                                                                                                                                                                                                                                                                            |

| CONFIG2 |                 |          | R/W    | 0x0004<br>()                                     | 0040                           | When 1 ADC values = 0<br>Bit 0 $\rightarrow$ ADC 0<br>Bit 1 $\rightarrow$ ADC 1<br>Bit 2 $\rightarrow$ ADC 2<br>Bit 3 $\rightarrow$ ADC 2<br>Bit 3 $\rightarrow$ ADC 3<br>Bit 4 $\rightarrow$ ADC 4<br>Bit 5 $\rightarrow$ ADC 5<br>Bit 6 $\rightarrow$ ADC 6<br>Bit 7 $\rightarrow$ ADC 7<br>Bit 8 $\rightarrow$ ADC 7<br>Bit 8 $\rightarrow$ ADC 8<br>Bit 9 $\rightarrow$ ADC 9<br>Bit 10 $\rightarrow$ ADC 10<br>Bit 11 $\rightarrow$ ADC 11<br>Bit 12 $\rightarrow$ ADC 12<br>Bit 13 $\rightarrow$ ADC 13<br>Bit 14 $\rightarrow$ ADC 14<br>Bit 15 $\rightarrow$ ADC 15 |

| CONFIG4                                   | 16 | 1  | R/W | 0x0005             | 0040 | 7 => rising edge write to AD9230 ADC<br>6 => 1 write to all ADC<br>5 => 0 write to AD9230<br>1 read from AD9230 . Data is at Stat<br>4 => 1 Reset ADC                                                                                  |

|-------------------------------------------|----|----|-----|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONFIG5                                   | 16 | 1  |     | 0x0006             | 0040 | 30 => Select ADC to write to         158 => Registers inside AD9230         70 => Data to write to register.                                                                                                                           |

| PTW                                       | 9  | 1  | R/W | 0x0007<br>()       | 0010 | PTW + 1 number of ADC sample to<br>include in trigger window.<br>PTW = Trigger Window (ns) * 250 MHz.<br>Minimum is 6.                                                                                                                 |

| PL                                        | 11 | 1  | R/W | 0x0008<br>()       | 0000 | Number of sample back from trigger point.<br>PL = Trigger Window(ns) * 250MHz                                                                                                                                                          |

| NSB                                       | 4  | 1  | R/W | 0x0009<br>()       | 0000 | 30: Read Back Path NSB<br>Number of sample before trigger point to<br>include in data processing. This include<br>the trigger Point. When NSB bit 3 is 1:<br>NSA has to be > NSB bits 1,0 by at<br>least 4 => NSA – (NSB bits 1,0) > 3 |

| NSA                                       | 15 | 1  | R/W | 0x000A<br>()       | 0005 | 80: Read Back Path NSA<br>Number of sample after trigger point to<br>include in data processing. <b>Minimum is 2</b><br>149: Trigger Path NSA                                                                                          |

| TET                                       | 12 | 16 | R/W | 0x000B -<br>0x001A | 0000 | Trigger Energy Thredhold.                                                                                                                                                                                                              |

| CONFIG6<br>(Monitored<br>Pedestal<br>Sum) | 16 | 1  | R/W | 0x001B             | 0000 | 13-10 MNPED : The number of ADC<br>sample to sum up is MNPED + 1. <b>Min is</b><br><b>4</b><br>9-0 PMaxPed : When an ADC Samples is<br>greater than this, bit 14 of the 14 bits (13-<br>0) Sum will be set.                            |

| CONFIG7<br>(Read Back<br>Pedestal<br>Sum) | 16 | 1  | R/W | 0x001C             | 0000 | 13-10 NPED : The number of ADC<br>sample is NPED + 1<br>9-0 MaxPed                                                                                                                                                                     |

| Test Wave<br>Form                         | 16 | 1  | R/W | 0x001D             | 0000 | Write to PPG. Read should immediately follow write.                                                                                                                                                                                    |

| ADC<br>Pedestal<br>Subtract               | 12 | 16 | R/W | 0x001E-<br>0x002D  | 0000 | Subtract from ADC(0-15) Count before<br>Summing                                                                                                                                                                                        |

| Config 3                                  | 16 | 1  | R/W | 0x002E             | 0000 | 15 : Sync Disable<br>(110) Trigger Path Processing Threshold                                                                                                                                                                           |

| STATUS 3                                  | 16 | 1  | R   | 0x002F             |      | FPGA core temp (DieTemp)                                                                                                                                                                                                               |

| STATUS 4                                  | 16 | 1  | R   | 0x0030             |      | 7-0 Result of ADC register readback                                                                                                                                                                                                    |

|                                           |    |    |     |                    |      |                                                                                                                                                                                                                                        |

# Appendix B

| Bias DAC Count | ADC Count With No Input (in hex) |

|----------------|----------------------------------|

| 4096           | 1000                             |

| 4000           | 1000                             |

| 3500           | 1000                             |

| 3300           | 66                               |

| 3100           | 173                              |

| 3000           | 1FB                              |

| 2900           | 281                              |

| 2800           | 30A                              |

| 2700           | 393                              |

| 2600           | 419                              |

| 2500           | 49E                              |

| 2400           | 526                              |

| 2300           | 5ae                              |

| 2200           | 632                              |

| 2100           | 6BA                              |

| 2000           | 741                              |

| 1900           | 7C6                              |

| 1800           | 850                              |

| 1700           | 8D5                              |

| 1600           | 95B                              |

| 1500           | 9E1                              |

| 1400           | A6B                              |

| 1300           | AFO                              |

| 1200           | B7B                              |

| 1100           | C00                              |

| 1000           | C86                              |

| 900            | DOE                              |

| 800            | D91                              |

| 700            | E19                              |

| 600            | EA1                              |

| 500            | F29                              |

| 400            | FAC                              |

| 300            | 1FFF                             |